NeTs: Medium: Energy-Efficient and Reconfigurable Wireless Networks through Hardware-Algorithm Co-Design

NYU Wireless P.I.s

Research Overview

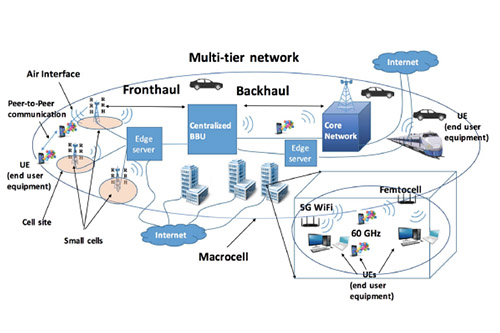

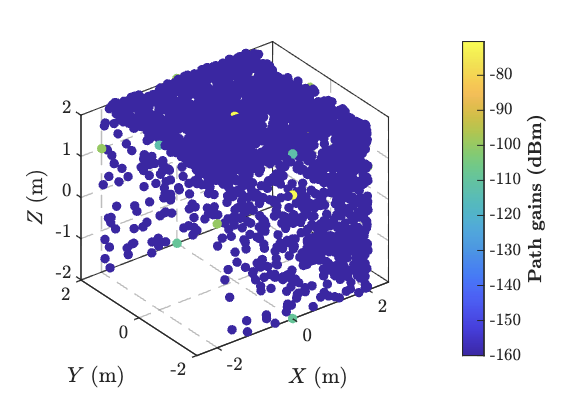

Power consumption is one of the most fundamental constraints in the design of any wireless communication system. Recent trends in wireless technology and its applications have now made power consumption considerations particularly urgent. For example, new cellular systems in the millimeter wave (mmWave) bands offer massive data rates but have come at the cost of staggering power consumption due to the need to support a large number of antennas at a high bandwidth. At the same time, new low-power technologies can now operate in the milli-watts of power but remain limited in data rates. As new embedded systems are increasingly demanding high data rates for sensor and camera data and cloud connectivity, fundamentally novel approaches will be needed to develop high-speed, but energy-efficient wireless networks. This project aims to develop such energy efficient wireless systems through a combination of analog and digital circuits, processing algorithms and communications theory.

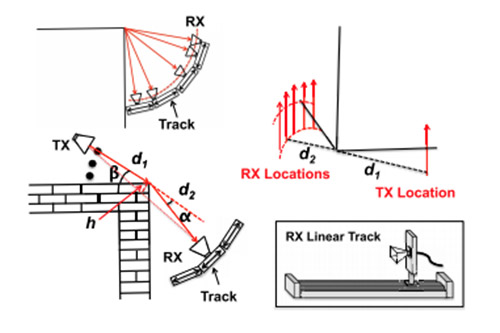

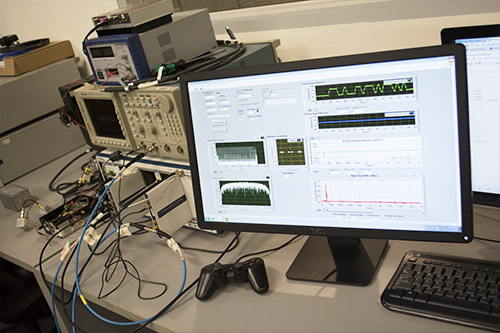

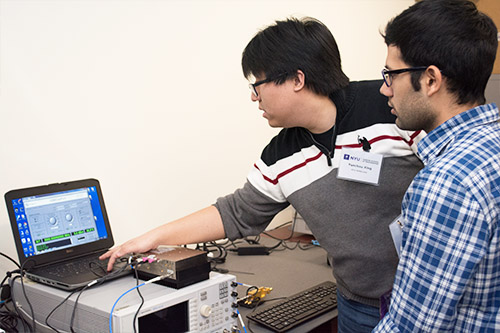

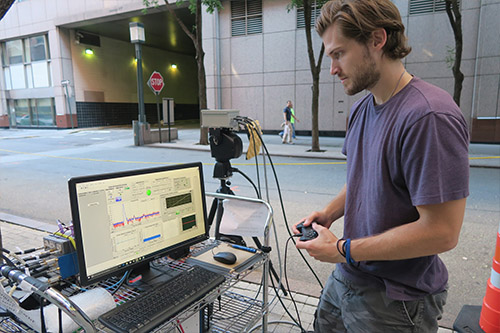

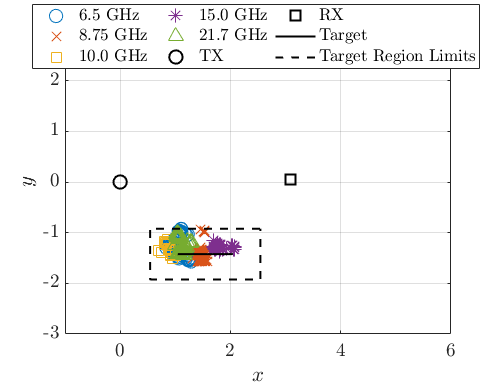

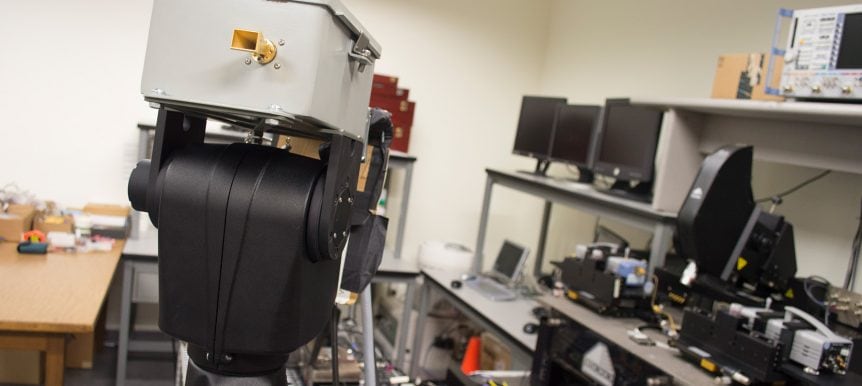

This project seeks to develop a reliable, energy-efficient high-speed wireless communication system through hardware and algorithm codesign, which allows for very low power digital and radio frequency (RF) hardware with imperfections such as non-linearities and high noise to be compensated by innovative communication algorithms and enables the adaptation of power trade-offs across different components based on channel and network conditions. The work is composed of four interrelated thrusts: Thrust 1 develops new low-power and reconfigurable RF components along with fundamental capacity bounds and signaling methods. Thrust 2 then develops energy-efficient methods to achieve these bounds with co-design of digital hardware and communications algorithms. Thrust 3 extends the methods to multiple antenna systems through novel compact low-power arrays and beamforming processing. Thrust 4 validates the developed methods and techniques with fabricated circuits and a novel low-power emulation platform.

This award reflects NSF’s statutory mission and has been deemed worthy of support through evaluation using the Foundation’s intellectual merit and broader impacts review criteria.

NYU WIRELESS Workshop Convened in January

NYU WIRELESS Workshop Convened in January Elza Erkip and Marwa Chafii Honored by Women in 6G

Elza Erkip and Marwa Chafii Honored by Women in 6G Postdoctoral Opportunities with NYU Wireless

Postdoctoral Opportunities with NYU Wireless